## Gábor Szőke

**Staff Analog Field Application Engineer**

# **PCB Layout**

## **PCB Layout: Regulatory requirements**

- Safety Agencies will control:

- The PCB material used

- Creepage distances shortest path between two parts along the SURFACE

- Grooves don't count if less than a certain width

- Clearance distances shortest path between two parts through air

- PCB slots can be used to increase creepage but not always clearance

- Safety, EN 62368-1 (replaces EN60950 Date Of Withdrawal 2019)

## **PCB Layout – Grounding and Ground Planes**

- Ideal Ground Plane is an Infinite Equipotential Surface

- Practical Ground Plane is a bounded 'almost Equipotential' Surface

- Return current in ground plane will follow the path of the outward bound conductor

- 'Image Current' minimises loop area and inductance, maximises capacitance and minimises impedance

- Do's and Don't's

- Don't put slots in the ground plane

- Ground planes are not possible on a single sided board (SSB)

- Take extra care to minimise the impedance in the ground connections in a SSB

- Low impedance from AGND to PGND is desirable

- Place as much grounded copper under the IC as possible

- Remember that DC tracks are an AC Ground

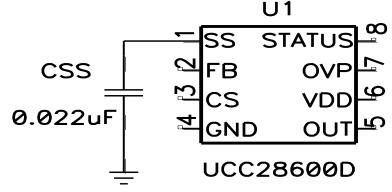

## **UCC28600**

8-pin Quasi-Resonant Green Mode PWM Controller

## **Efficiency Requirements**

- Energy Star®

- Single voltage external AC-DC and AC-AC power supplies

- Power supplied to be labeled with efficiency grade

- Active mode efficiency based upon calculation of the simple average of 25%, 50%, 75%, and 100% of full rated power at nominal input

| Rated Output Power (P <sub>OUT</sub> ) | Minimum Efficiency (η)                             |

|----------------------------------------|----------------------------------------------------|

| $0W \leq P_{OUT} \leq 1W$              | $\eta \ge 0.48 \text{ x P}_{\text{OUT}} + 0.14$    |

|                                        | $\eta \ge 0.497x \; P_{OUT} \; + 0.067$            |

| $1W < P_{OUT} \le 49W$                 | $\eta \ge [0.0626 \text{ x } ln(P_{OUT})] + 0.622$ |

|                                        | $\eta \ge [0.0750 \text{ x ln}(P_{OUT})] + 0.561$  |

| $49W < P_{OUT} \leq 250W$              | $\eta \geq 0.87$                                   |

|                                        | $\eta \geq 0.86$                                   |

| P <sub>IN</sub> = 100W                 | PF ≥ 0.9 @ 100% load                               |

$V_{OUT} < 6V, I_{OUT} \ge 0.55A$

No-Load (Stand By) mode measured with open output

| Rated Output Power (P <sub>OUT</sub> ) | Maximum Input Power (P <sub>IN</sub> ) |  |

|----------------------------------------|----------------------------------------|--|

| 0W ≤ P <sub>OUT</sub> < 50W            | $P_{IN} \leq 0.3W$                     |  |

| OVV S POUT > SOVV                      | (0.5W for AC/AC)                       |  |

| $50W \le P_{OUT} \le 250W$             | $P_{IN} \leq 0.5W$                     |  |

#### UCC28600: Features

- 8 Pin Quasi-Resonant Flyback Green Mode Controller

- Current Mode Controller

- Quasi-Resonant Mode For Reduced EMI And Low Switching Losses (Valley Switching)

- Low Stand By Current For Low System No-load Power Consumption

- Protection Features:

- Programmable Line Over Voltage Protection

- Programmable Load Over Voltage Protection

- Internal Over Temperature Protection

- Cycle By Cycle Power Limit

- Over Current Hiccup Restart Mode

- Green Mode STATUS Pin To Disable PFC During Light Load

- 1A Sink/0.75A Source TrueDrive™ Gate Drive Output

- Multi-mode Operation For Energy Efficiency Over Entire Range Of Operation

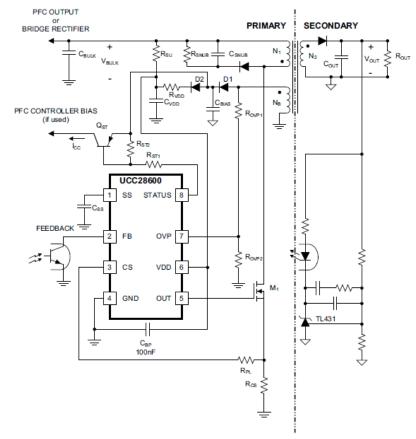

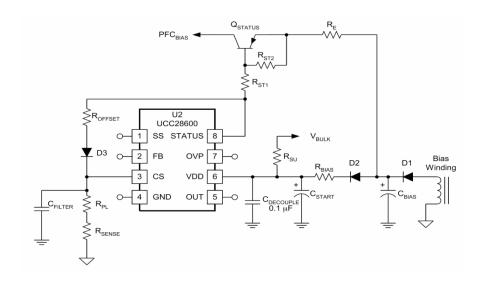

### **UCC28600**

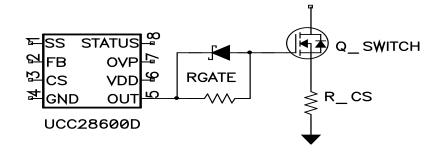

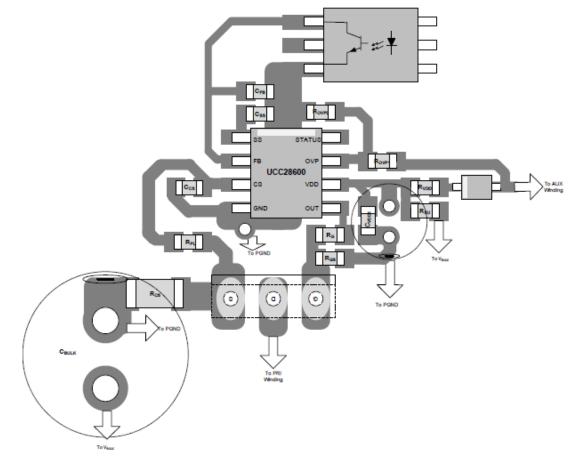

Simplified Application

Figure 13. Simplified Application

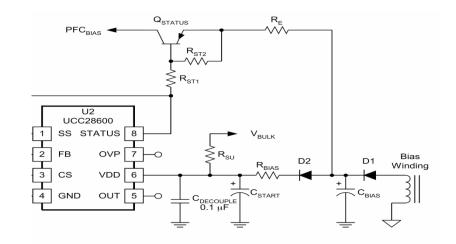

### UCC28600: VDD

- Low start up current ( $12\mu A$  typical) enables use of high value start up resistors from rectified input bus ( $R_{SU} = 2 + M\Omega$ )

- PFC stage will be off at start up

- Operating energy supplied by auxiliary bias winding

- Light load conditions, bias winding voltage will be lower than full load conditions

- C<sub>BIAS</sub> must be large enough to hold up VDD during burst packet period

- Use a 0.1μF ceramic capacitor to GND pin for high frequency filtering

## **UCC28600: VDD (cont.)**

- Additional C<sub>START</sub>/D<sub>2</sub> required to isolate STATUS from start up resistors (R<sub>SU</sub>)

- When VDD < UVLO internal floating gates divert startup current from VDD

- Series resistor with bias winding to limit transients from leakage inductance and drain capacitance

- Needed To Prevent OVP Triggering During Transients

$$R_{BIAS} = \frac{\pi}{4} \cdot \frac{N_{B}}{N_{P}} \cdot \left[ \frac{V_{DSovershoot} \cdot f_{max} \cdot \sqrt{L_{leak} \cdot (C_{DRAIN} + C_{SNUB})}}{I_{DD} + C_{ISS} \cdot V_{GATE} f_{max}} \right]$$

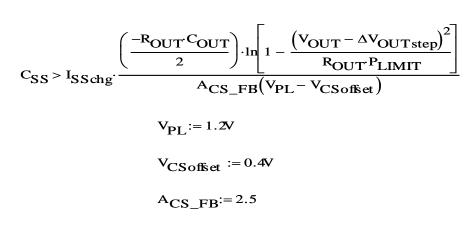

### UCC28600: SS

- All faults discharge SS to GND (except PL)

- C<sub>SS</sub> must be chosen so as to not trigger power limit when charging output caps

- Layout is important

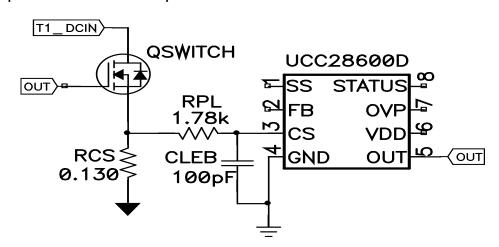

### UCC28600: CS

- Power Limit

- Triggered at V<sub>CS</sub> = 0.8V

- Design Calculator uses "Pout, max limit" as Power Limit set point

- Line dependent

- Uses current sourced by OVP to add an offset proportional to line voltage

- DCM converter but CS has ramp-on-a-step waveform due to power limit offset

- Will not trigger SS discharge

- Over current shutdown

- Triggered when  $V_{CS} = 1.25V$

- R<sub>PL</sub> and capacitor to GND for noise filter

### UCC28600: OVP

- Provides information proportional to the drain voltage

- Valley Detection

- Line over-voltage

- Note: spec has very wide range

- Load over-voltage

- Provides internal I<sub>LINE</sub> current

- Crucial to have bias windings well coupled to both primary and secondary

$$R_{OVP1} = \frac{\frac{N_B}{N_P} \cdot V_{BULKshutdown}}{450 \,\mu A}$$

$$R_{OVP2} = \frac{R_{OVP1}}{\left(\frac{N_B}{N_S} \cdot \frac{V_{OUTshutdown} + V_F}{3.75 V}\right) - 1}$$

## **UCC28600: OVP (cont.)**

| OVP                       |                                                        |                                                                                   |                                                                                                                                                                             |                        |  |

|---------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| EVENT                     | EVENT CONDITIONS                                       |                                                                                   | RESULT                                                                                                                                                                      |                        |  |

| LINE OVER<br>VOLTAGE      | OUT = HIGH; OVP IS<br>PROPORTIONAL TO<br>LINE VOLTAGE  | IF OVP CLAMPED TO<br>0V AND SOURCING<br>450uA<br>LINE OVER VOLTAGE<br>IS DETECTED | - TURNS OFF OUTPUT - AUX WINDING FALLS - VDD FALLS BELOW UVLO - SS DISCHARGES - TURN ON WHEN SS RE-CHARGES                                                                  | CHECKED<br>EVERY CYCLE |  |

| OUTPUT<br>OVER<br>VOLTAGE | OUT = LOW; OVP IS<br>PROPORTIONAL TO<br>OUTPUT VOLTAGE | IF OVP = 3.75V<br>OUTPUT OVER<br>VOLTAGE IS<br>DETECTED                           | - TURNS OFF OUTPUT - AUX WINDING FALLS - VDD FALLS BELOW UVLO - SS DISCHARGES - TURN ON WHEN SS RE-CHARGES                                                                  | CHECKED<br>EVERY CYCLE |  |

| VALLEY<br>DETECT          | OUT = LOW                                              | OVP DETECTS<br>DEMAGNETIZED CORE<br>FROM 0V TRANSITION                            | - QR TAKES PRECEDENCE  - OUTPUT TURNED ON IF RUNNING < 130kHz  - AT 130kHz, TURN ON AT NEXT VALLEY THAT WOULD RESULT IN fs < 130kHz  - TURN-OFF BY PEAK CURRENT PWM CONTROL | CHECKED<br>EVERY CYCLE |  |

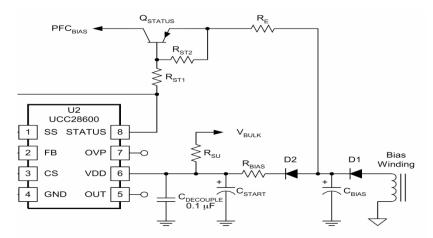

### UCC28600: STATUS

- Active High: drives base of PNP to provide bias to PFC controller

- High during UVLO and SS

- PFC stage off

- Select R<sub>ST1</sub> and R<sub>ST2</sub> to operate Q<sub>STATUS</sub> in saturation/cutoff

- Careful selection of R<sub>ST1</sub> and R<sub>ST2</sub> so Q<sub>STATUS</sub> doesn't turn on during green-mode

- Can be used to eliminate audible noise

### UCC28600: OUT

- Internally Clamped To 13V Or VDD Whichever Is Lower

- TrueDrive Provides 1A+ Of Current Sink Where It Counts, During MOSFET Turn Off

- Use parallel diode to speed up turn off

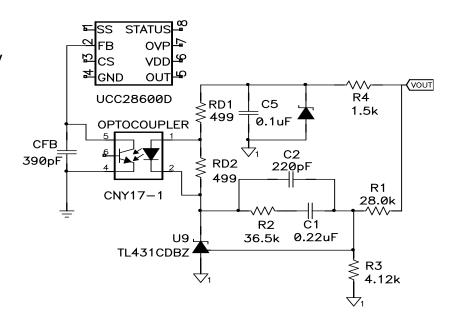

### UCC28600: FB

- Collector of Opto tied directly to FB

- FB has internal 20kΩ pull-up resistor to the 5V reference

- Maximum duty cycle is when FB is high and zero duty cycle is when FB is low.

- Capacitor on FB provides delay time for over load protection: 390pF max value

- FB internal thresholds play a key role in determining operating mode

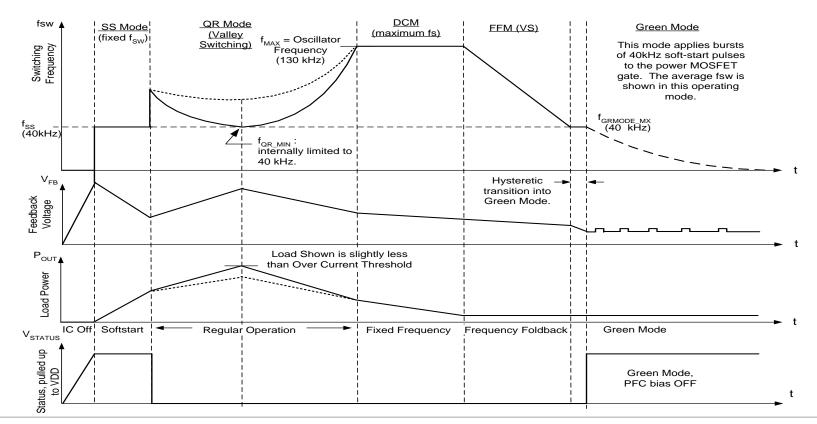

### **UCC28600: MODES**

- V<sub>FB</sub> Thresholds Determine Operating Mode

- Mode Depends Upon Boundaries Set By

- Magnetizing inductance

- Reflected output voltage

- Input Voltage Range

- Minor manipulations can be made by V<sub>CS</sub> through iterative selection of

- $-R_{CS}$

- $-R_{PL}$

- R<sub>OVP1</sub>

- $-R_{OVP2}$

## UCC28600: MODES (cont.)

- UCC28600 always operates in current mode control

- FB controls operating mode

- $-30\% \le I_{1,OAD} \le 100\%$ : QR or DCM

- 2V ≤ FB ≤ 4V

- Clamped f<sub>MAX</sub>

- Valley switching

- $0.4V \le CS \le 0.8V$

- $-10\% \le I_{1,OAD} \le 30\%$ : FFM

- 1.4V ≤ FB ≤ 2V

- $40kHz \le f_{MAX} \le 130kHz$

- Valley switching

- CS = 0.4V

- $-0\% \le I_{1,OAD} \le 10\%$ : Burst

- $0.5V \le FB \le 1.4V$

- Switching within burst packets is 40kHz

- CS < 0.4V

## UCC28600: MODES (cont.)

20

## UCC28600: MODES (cont.)

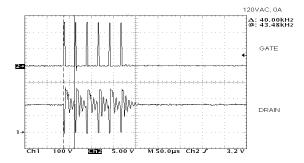

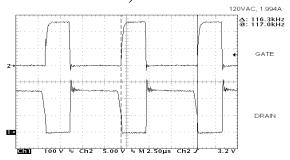

#### GREEN MODE 120VAC IN, 0.0A

Critical Conduction 120VAC IN, 1.99A

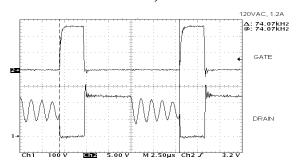

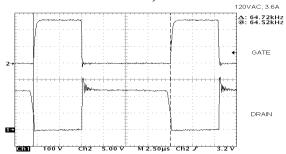

#### FFM 120VAC IN, 1.2A

QR MODE 120VAC IN, 3.6A

## **Consider Layout Before the Board is Built**

- Minimize the high current loops to reduce parasitic capacitances and inductances.

- But do not make traces with a high dv/dt too wide as this will create a very good E-field antenna.

- Separate the IC signal ground from the high current power ground in order to isolate the noise away from the IC substrate. The separate grounds should be tied together at the input capacitor on the primary side.

- Returning the sense resistor to the input capacitor, instead of to the ground plane under the IC, is also required for a successful design.

- The decoupling capacitor on VDD must be placed as close as possible to the VDD and GND pins of the IC.

- The FB trace should be short and as far away from noise as possible.

- · Use a short, wide trace width for the gate drive

- Use a small value gate drive resistor in series with the gate drive to control the turn on transition time and reduce the dv/dt ringing in this node.

- A 10k resistor is placed between the gate of the MOSFET and ground to discharge the gate capacitance and protect against inadvertent dv/dt triggered turn-on.

- Adding a small capacitor, C<sub>FILTER</sub>, to the CS pin will create an RC low pass filter in conjunction with the power limit resistor, R<sub>PL</sub>, and will improve noise immunity at the current sense pin.

Figure 25. Partial Layout Example Showing Component Placement